Big photo: The semiconductor industry is approaching a significant milestone because TSMC prepares to expand the physical scale of its chip packaging technology. In its recent North American Technology Seminar, the company made a detailed plan for a new generation of cououn (chip-on-verm-on-possession) technology, which currently makes the assembly of multi-spulet processor much larger than those in production.

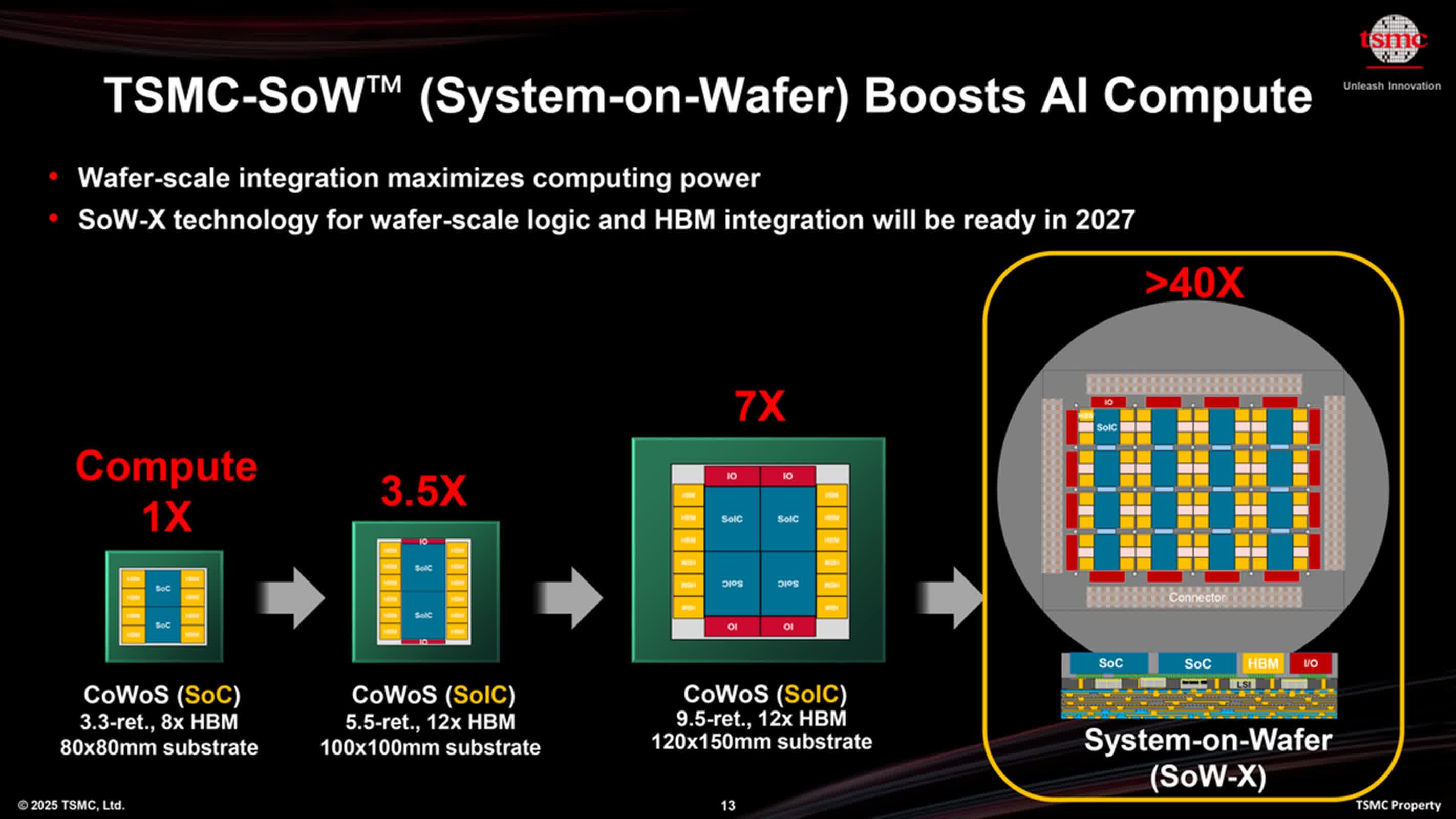

Today’s high-end processors, especially those who power the data centers and AI workloads, rely on multi-chiplet designs to fulfill the increasing demands for performance and memory bandwidth. Current Curos Solutions of TSMC can adjust the interpreting from 2,831 mm to interpreting, more than three times the size of a standard photomask retail, which is limited to 830 – 858 mm by EUV lithography obstacles.

This technique is already being used in products such as instinct Mi300x of AMD and B200 GPU of NVIDIA, which combines large compute chipsets with piles of high-bandwidth memory.

However, the AI and high-demonstration continue to increase complexity as computing applications, and even more hunger for silicone is increasing. To address it, TSMC is Developing A new council-lasing technique, which is set to launch earlier next year, supports the interpreting, which is large as 4,719 mm–is required to measure rehabited 5.5 times ratical range-and 100 × 100 mm. This will allow up to 12 stacks of high-bandwidth memory, which is an important step from current capabilities.

The TSMC projects that will deliver more than three and a half times of the performance of today’s leading designs composed with this technique, potentially meet the needs of upcoming processors such as Rubin GPUS of NVIDIA.

Further, TSMC plans to push the envelope with another larger package: a 7,885 mm mm interpreting 120 × 150 mm mounted on a substrate, slightly larger than a standard CD case. This represents a 9.5-fold increase on the ratical range and almost doubles the area of the company’s previous 8X-yetical package.

Such a huge assembly can host four 3D-stacked system-on-revised chips, twelve HBM4 memory stacks, and many input/output dying, which sets a new benchmark for performance and integration.

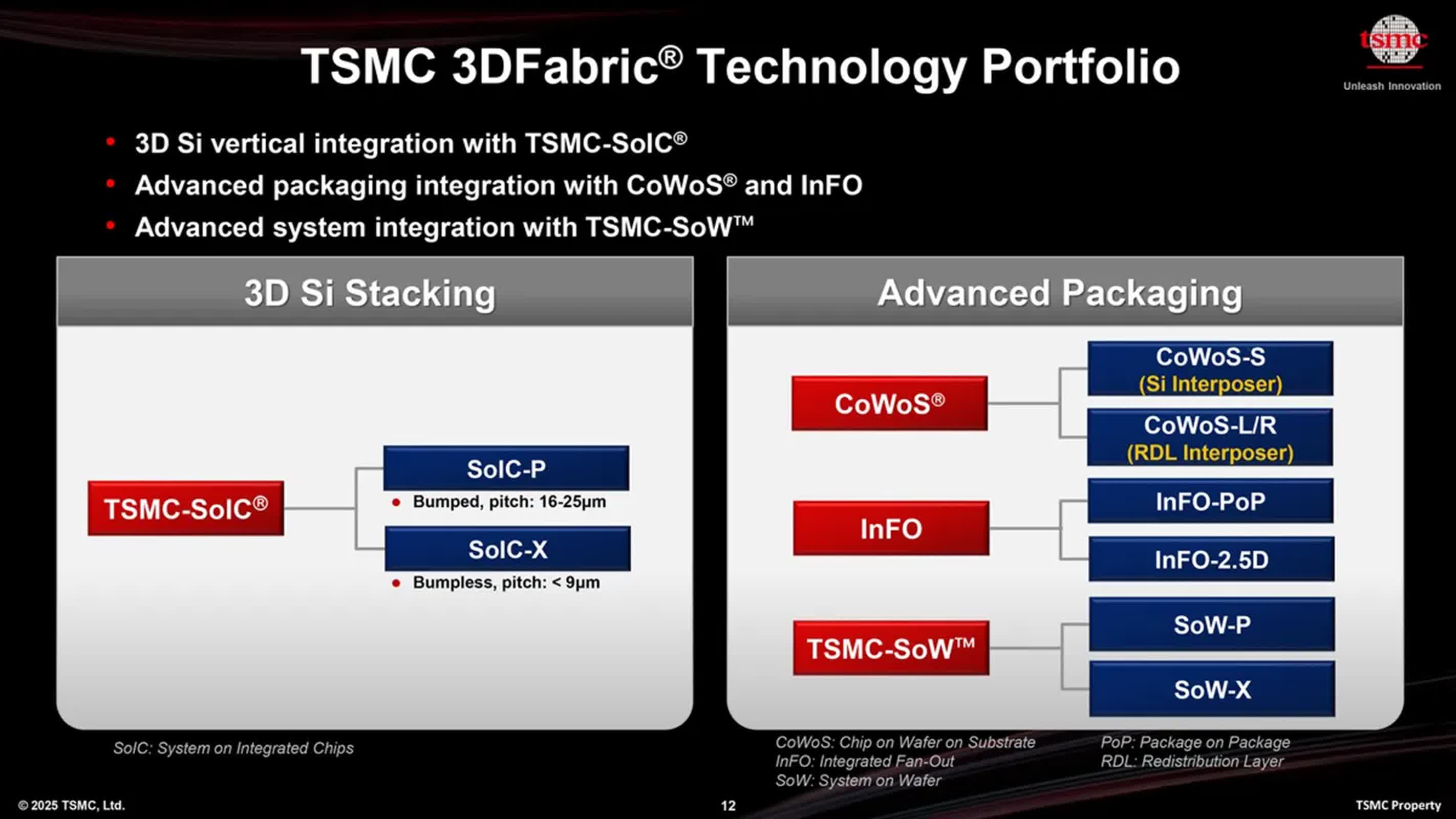

For customers with the most extreme performance requirements, TSMC is also offering its system-on-verge (Sow-X) technology, which enables the integration of the entire wafers into the same chip. While only a few companies, such as Cerebra and Tesla, currently use wafer-level integration for special AI processors, TSMC estimates widely adoption as the demand for super-shaped chips increases.

Engineering challenges related to these behemoth processors are enough. Innovative solutions are required to power large, multi-chiplet assembly, as they can attract kilowatt power to handle traditional server design.

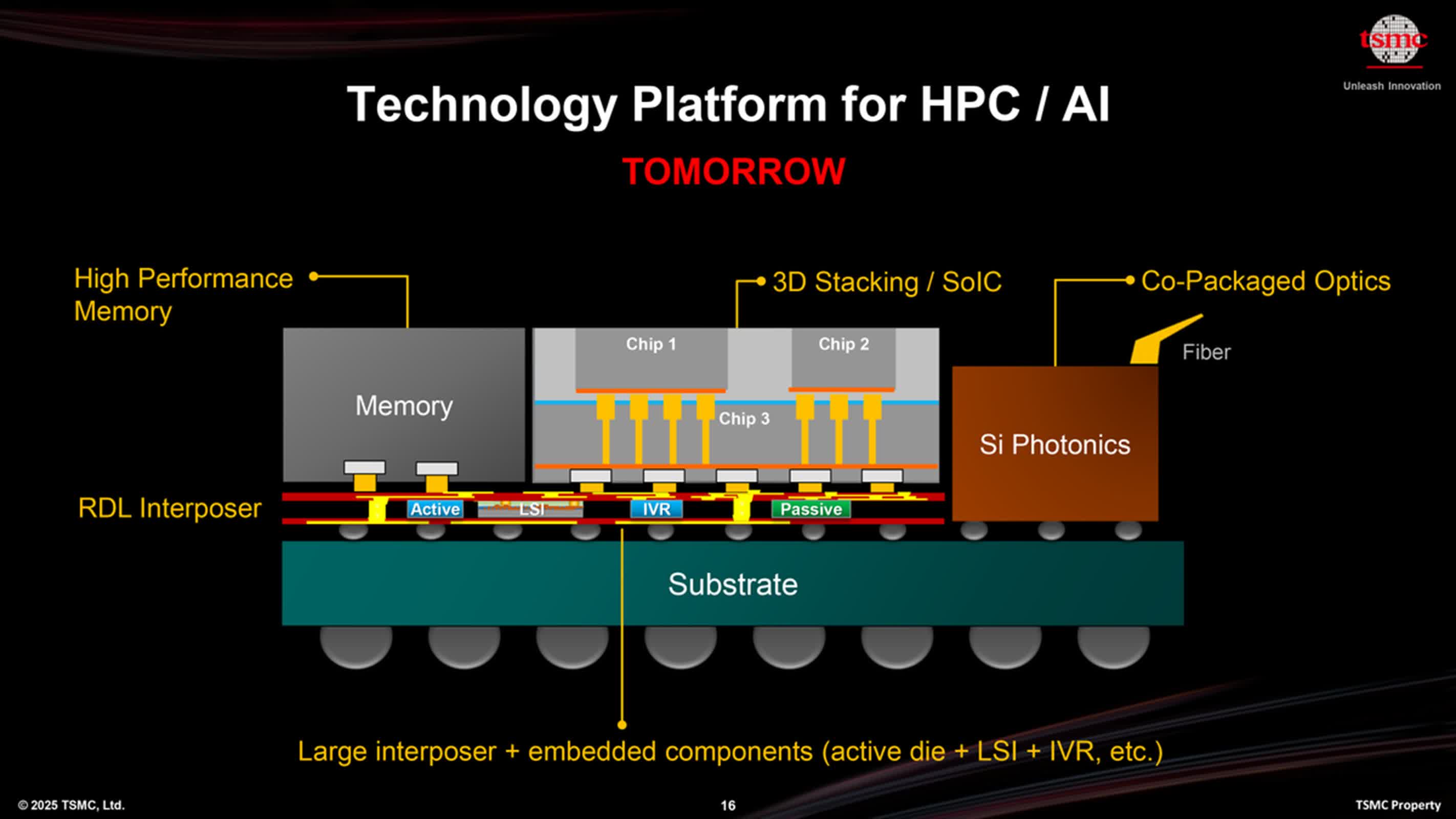

To deal with this, the TSMC is integrating the advanced power management circuit directly into the chip package. Using its N16 Finfet technology, the company embedded the monolithic power management ICS and on-wheeler inductors in the keouse-el substrate, allowing the power to be efficiently rooted through the package.

This approach reduces electrical resistance and improves the integrity of electricity, leading to a rapid reaction to dynamic voltage scaling and changing workload. Embedded deep trench capacitors further stabilize electrical performance, filter the voltage rapid and ensure reliable operations under heavy computational loads.

These advance systems-a comprehensive change towards the system-level co-ease, showing power distribution, packaging and silicone design are considered as interconnected elements rather than different concerns.

However, sometimes the move of big chip packages is not without its complications. The physical size of the new substrates, especially 100 × 100 mm and 120 × 150 mm format, existing module standards such as OAM 2.0, is advancing the boundaries, and new systems and board design may require approaches.

Thermal management is another important challenge. As processors grow in size and power consumption, they generate heavy amounts of heat. Hardware manufacturers are searching for advanced cooling techniques including direct liquid cooling and immersion to run these chips efficiently.

TSMC has already worked with partners to develop immersion cooling solutions for data centers. These solutions can reduce energy consumption and also stabilize chip temperature under intensive charge. However, integrating these cooling technologies directly into chip package is a challenge for the future.